상품상세정보

▶ Overview

VeriTiger®-V9P is a pretty agile and easy bring-up prototyping system from HyperSilicon, using Xilinx Virtex UltraScale+ XCVU9P FPGA. VeriTiger®-V9P delivers high performance, fast running speed and flexible scalability to accelerate software development, system verification and validation. Through the Protowizard® software to manage prototyping runtime resource and Semu® software to deliver highest debug productivity, VeriTiger®-V9P can significantly reduce the digital IC development time.▶ Key Features

Pretty agile, Easily bring up

VeriTiger®-V9P is a lightweight desktop prototyping platform, based on single XCVU9P FPGA. Only 3kg makes it is so easy to place or move VeriTiger®-V9P.High speed compile and run, Cost-effective

hsSynth, the high speed parallel compile solution, which speeds up the synthesis process multiple times is supported and VeriTiger®-V9P runs up to 100MHz for advanced design prototyping.Rich Connectivity and 100+ Daughter Cards

Rich Connectivity is built in VeriTiger-V9P for 100+ ready daughter cards provided by HyperSilicon®. Flexible interfaces deliver high flexibility for clocking, debug and host interface, hsDman, the daughter card management software researched and developmented by HyperSilicon®, can effectively monitor and manage abundant daughter cards.▶ Specification

- FPGA Devices : Xilinx Virtex UltraScale+ XCVU9P FPGA (XCVU9P-2FLGA2104I x 1)

- 15.5 Million Estimated ASIC Gates

- 2586K System Logic Cells

- FPGA Memory 345.9Mb(Block RAM 75.9Mb+Ultra RAM 270Mb)

- 6840 DSP Slices

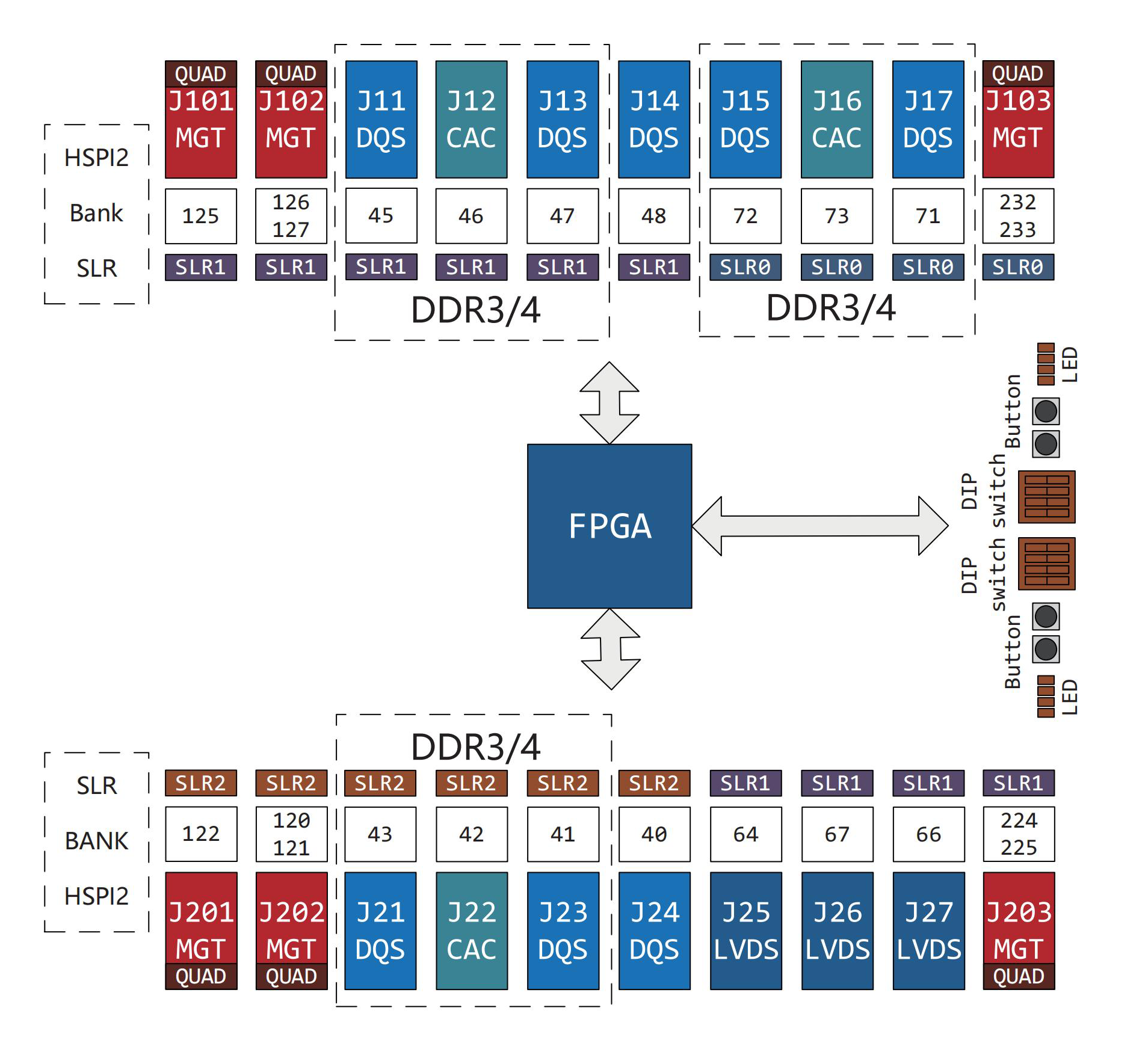

- Connector Resources : 720 High-performance I/Os in total in HSPI2 Connectors

- 6 HSPI2-MGT Connectors, Offering 40 Lanes GTY Channel

- 2 QSFP Interfaces, Offering 8 Lanes GTY Channel

- 8 HSPI2-DQS Connectors

- 3 HSPI2-CAC Connectors, Supporting 3 DDR3/DDR4

- 3 HSPI2-LVDS Connectors, Offering71 LVDS Differential Pairs

- 2 Independent Buttons, 1 Four-digit DIP Switch, 4 User-defined LED Lights

- Clock Resources :

- 4 Programmable Differential Clocks

- 2 Clocks at 20MHz, 2 Clocks at 27MHz

- 2 SI5338 MMCX Differential Clock Inputs

- 1 SI5338 MMCX Differential Clock Output

- 2 MGT Differential Clocks at 100MHz

- Direct Connect-to FPGA Differential Clocks Offered By 2 Pairs of MMCX

- 3 Transceiver Refclks at 100MHz

- 1 Multi-FPGA Shared and Global Programmable Differential ZCLK Clocks

- Platform Parameters

- Dimensions: L223mm, W340mm, H91mm

- Weight: 3.0 Kg

- Max Power Consumption: 120W

▶ Datasheet

▶ Strong softwares

- ProtoWizard® ProtoWizard® is the runtime software researched and developed by HyperSilicon® to manage prototyping resource. ProtoWizard® delivers high performance in environment construction, resource management, security monitoring, system configuration, etc. in the process of FPGA prototyping. It helps users establish the prototyping environment efficiently and reduces bring-up time.

- Multi-Design And Multi-User

- Multi-Veritigers Management

- Turn Off Anytime And Anywhere

- Online Firmware Update

- Hardware Self-Test

- HsDman HsDman is the daughter card management software researched and developmented by HyperSilicon® for our ready daughercards provided to users. HsDman monitors and manages the present 100+ daughter cards effectively and assists verification team to save prototype development costs and resources.

- Pin Mapping

- Daughter Card Library

- Mother Board Library

- Transfer Card Library

- hsSynth hsSynth® innovates a new way to segment the large-scale design into specified amount modules, and then parallel compile these modules to achieve multifold speed-up of the synthesis process. Only the modified sub-modules will be re-synthesized when the design iterated, which greatly shortens the iterative synthesis process. For multiple iterations in the design, hsSynth only needs to re-synthesize the sub-modules of the iterations, which greatly accelerates the iterative synthesis process.

- Top-down

- Bottom-up

- Incremental Compilation

- Multifold Speed-up

- hsTrace Compared with FPGA integrated logic analyzer which delivery a poor sampling depth and transmission speed due to the waveform data occupies FPGA RAM, hsTrace deep debug tool includes many advanced features, including the sampled data is stored in an 8GB external DDR,the waveform data is transfered through ethernet to PC rapidly and provide up to 1G data dump depth.

- External RAM

- Transfer by Ethernet

- UP to 1G Dump Depth

Highlights

Highlights

At the same time, hsSynth provides a "top-down" synthesis mode for FPGA prototype verification to obtain the highest running speed and maximum utilization efficiency of FPGA. Provides a "Bottom-up" synthesis mode for emulation to achieve the maximum consistency with RTL code and maximum debug visibility.

Highlights

Highlights

▶ I/O Architecture

▶ What's Included

- ATX Power Adaptor: Huntkey Power HYPER 550B

- Ethernet Cable 3m: Gigabit Network Cable

- HSPI2-037-GPLP-C12: GPIO Loopback Test Card

- HSPI2-044-GPIO-B12: HSPI2 to GPIO Card

- HYDT-036-RIS3-A11: Riser3 Lift Protection Card

- HYDT-042-MGLP-D11: MGT Loopback Test Card

배송안내

● 결제일로부터 1~3주 안에 배송됩니다.

● 제조사 재고가 부족하여 3주 안에 배송이 어려울 경우 메일로 안내해 드리니 참고하시기 바랍니다.

교환 및 반품안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 교환 및 반품 처리 요청하면 교환 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 교환 및 반품 처리됩니다.

환불안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 환불 요청하면 환불 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 환불수수료(5천원+판매가의1%)을 제외한 나머지 금액을 환불 처리해 드립니다.

장바구니 담기

상품이 장바구니에 담겼습니다.

바로 확인하시겠습니까?

찜 리스트 담기

상품이 찜 리스트에 담겼습니다.

바로 확인하시겠습니까?