상품상세정보

▶ Product Description

The Terasic DE5-Net Stratix V GX FPGA Development Kit provides the ideal hardware solution for designs that demand high capacity and bandwidth memory interfacing, ultra-low latency communication, and power efficiency. With a full-height, 3/4-length form-factor package, the DE5-Net is designed for the most demanding high-end applications, empowered with the top-of-the-line Altera Stratix V GX, delivering the best system-level integration and flexibility in the industry.

The Stratix® V GX FPGA features integrated transceivers that transfer at a maximum of 12.5 Gbps, allowing the DE5-Net to be fully compliant with version 3.0 of the PCI Express standard, as well as allowing an ultra low-latency, straight connections to four external 10G SFP+ modules. Not relying on an external PHY will accelerate mainstream development of network applications enabling customers to deploy designs for a broad range of high-speed connectivity applications. For designs that demand high capacity and high speed for memory and storage, the DE5-Net delivers with two independent banks of DDR3 SO-DIMM RAM, four independent banks of Cypress QDRII+ SRAM or functional compatible SRAMS provided by GSI and ISSI, high-speed parallel flash memory, and four SATA ports. The feature-set of the DE5-Net fully supports all high-intensity applications such as low-latency trading, cloud computing, high-performance computing, data acquisition, network processing, and signal processing.

Compatible SRAMs functionality similar to the Cypress QDRII+ SRAMs

| IS61QDPB44M18A1-450M3LI |  | CY7C25632KV18-500BZXI | |

| GS8662DT20BGD-550 |

Component Solution for Altera FPGAs

| Power Solution for Altera FPGAs |  | X2Y Power Decoupling Solution | |

| Passive Component Solution for Altera FPGAs |

▶ Specifications

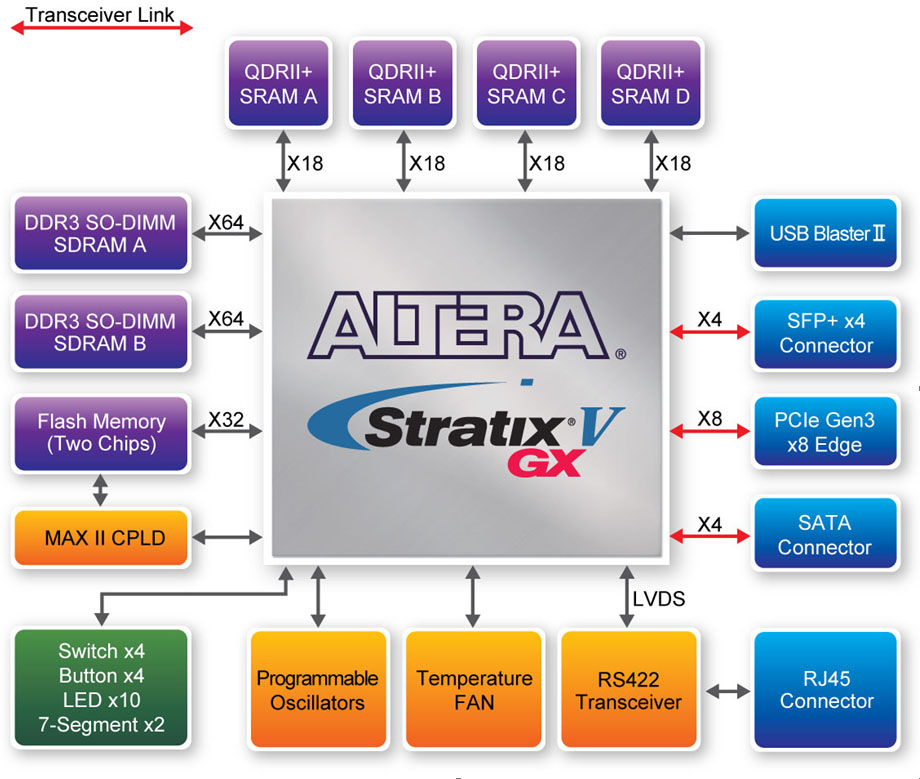

FPGA

| FPGA Altera Stratix® V GX FPGA (5SGXEA7N2F45C2) FPGA Configuration On-Board USB Blaster II or JTAG header for FPGA programming Fast passive parallel (FPPx32) configuration via MAX II CPLD and flash memory |

Memory

| Memory Two Independent DDR3 SODIMM Socket, Up to 8GB 800 MHz or 4GB 933 MHz for each socket Four Independent 550MHz SRAM, 18-bits data bus and 72Mbit for each 256MB FLASH |

Communication

| Communication Ports Four SFP+ connectors PCI Express (PCIe) x8 edge connector (includes Windows PCIe drivers) One RS422 expansion header |

Others

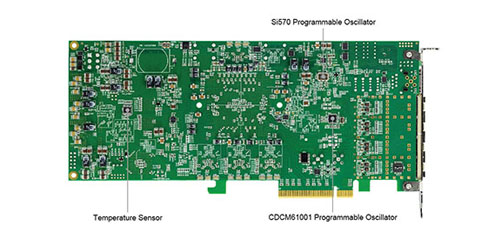

| General user input / output: 4 LEDs 1 LED Array 4 push-buttons 4 slide switches 2 seven-segment displays SMA clock input / output On-Board Clock 50MHz Oscillator Programmable oscillators Si570, CDCM61001 and CDCM61004 System Monitor and Control Temperature sensor Fan control Power PCI Express 6-pin power connector, 12V DC Input PCI Express edge connector power Mechanical Specification PCI Express standard height and 3/4-length |

Block Diagram

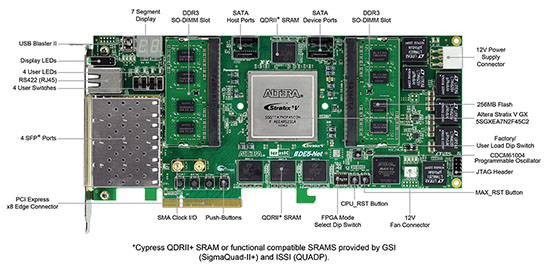

▶ Layout

- Size : 239 x 107 mm

▶ Resources

Download

Document

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE5-Net User Manual | 1.1.0 | 9516 | 2018-01-26 |  |

CD-ROM

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE5-Net System CD | 2.0.0 | 2018-01-26 |

BSP(Board Support Package) for Altera SDK OpenCL 16.1

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE5-Net OpenCL BSP for Windows | 1.1.0 | 2017-05-25 | ||

| OpenCL User Manual | 1.0.2 | 2272 | 2017-04-26 |  |

| DE5-Net OpenCL BSP for Linux | 1.0.2 | 2017-04-26 |

BSP(Board Support Package) for Altera SDK OpenCL 16.0

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE5-Net OpenCL BSP for Windows | 2016-12-20 | |||

| OpenCL User Manual | 2174 | 2016-11-01 |  | |

| DE5-Net OpenCL BSP for Linux | 2016-11-01 |

BSP (Board Support Package) for Altera SDK OpenCL 14.0/14.1 - Network Platform

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| User Manual for OpenCL - Network Platform | 2703 | 2015-07-17 |  | |

| DE5-Net Network BSP for Windows | 2015-07-17 | |||

| DE5-Net Network BSP for Linux | 2015-07-16 |

BSP(Board Support Package) for Altera SDK OpenCL 14.0/14.1

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| DE5-Net OpenCL BSP for Windows | 2015-05-05 | |||

| OpenCL User Manual | 1.0 | 2502 | 2014-11-11 |  |

| DE5-Net OpenCL BSP for Linux | 2014-11-11 |

BSP(Board Support Package) for Altera SDK OpenCL 13.1

| Title | Version | Size(KB) | Date Added | Download |

|---|---|---|---|---|

| OpenCL User Manual | 13.1 | 3009 | 2014-11-11 |  |

| DE5-Net OpenCL BSP for Windows | 2014-02-07 | |||

| DE5-Net OpenCL BSP for Linux | 2014-02-07 |

More resources about IP and Dev. Kit are available on Altera User Forums.

DE5-Net Tools

System Builder

The System Builder allows users to create a Quartus II project that includes the top-level design file, pin assignments, and I/O standard setting for the board.

Reference Designs

The FPGA System CD Kit contains various reference designs with source code and complete document reducing the development cycle.

- DDR3 SDRAM Test

- SigmaQuad-II+/QDRII+/QUADP Test

- PCIe Express Communication

- Programmable Oscillator

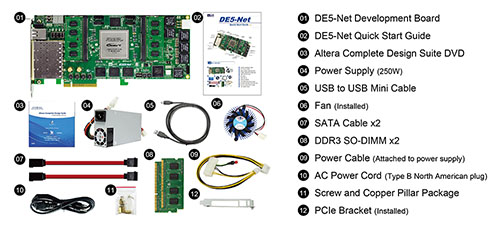

▶ Kit Contents

Quartus design software license is not included in this kit.

배송안내

● 이니프로에서 판매하는 모든 제품은 이니프로에서 통관 처리후 우체국 택배로 배송됩니다.

● 국내재고가 있는 경우 결제일로부터 3~4 영업일 안에 국내재고가 없는 경우 결제일로부터 3주 안에 배송됩니다.

● 현재 국내재고가 있는지 확인하시려면 1:1 문의 게시판에 남겨주시거나 sales@inipro.net 으로 메일을 보내주시기 바랍니다.

● 제조사 재고가 부족하여 3주 안에 배송이 어려울 경우 메일로 안내해 드리니 참고하시기 바랍니다.

교환 및 반품안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 교환 및 반품 처리 요청하면 교환 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 교환 및 반품 처리됩니다.

환불안내

● 제품 수령후 7일이내에 이니프로 고객센터에 연락하여 환불 요청하면 환불 가능합니다.

● 제품은 박스 상단에 아이디 또는 성함 등을 표기한 후 쇼핑몰 하단의 주소 및 연락처로 택배 발송해 주시기 바랍니다.

● 제품 및 제품포장 박스 등에 손상된 부분이 없는지 고객센터에서 확인한 후 환불수수료(5천원+판매가의1%)을 제외한 나머지 금액을 환불 처리해 드립니다.

AS안내

● 제품 보증 기간이 90일인 제품입니다.

● 납품후 90일 이내에는 무상 AS, 90일 이후에는 유상 AS 처리됩니다.

장바구니 담기

상품이 장바구니에 담겼습니다.

바로 확인하시겠습니까?

찜 리스트 담기

상품이 찜 리스트에 담겼습니다.

바로 확인하시겠습니까?